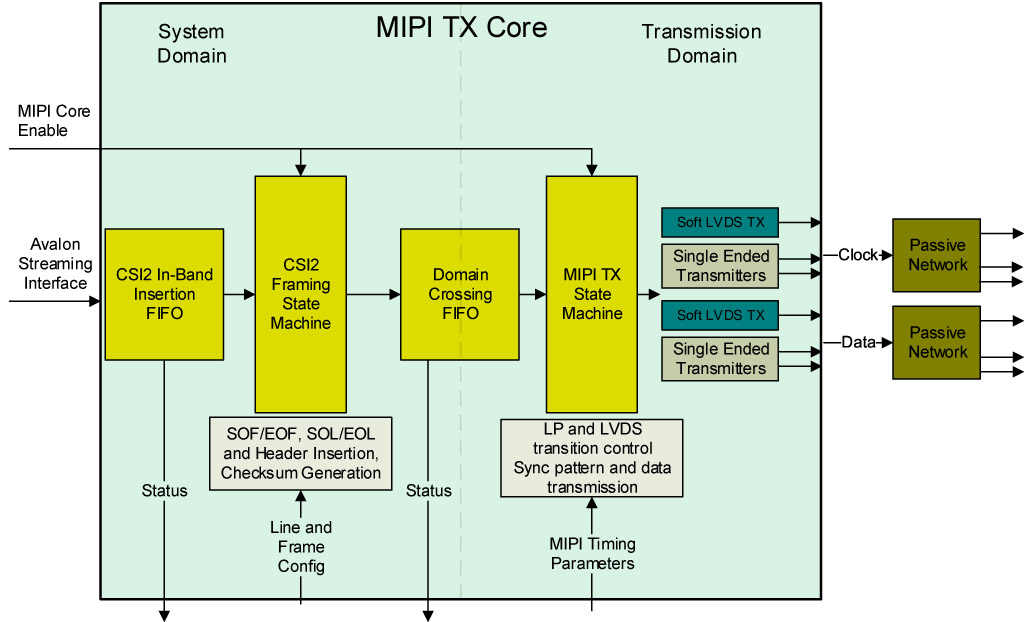

The Foresys MIPI CSI2 Tx Core provides a fast path to integrating Image Sensors into a wide variety of products based on Altera devices. It is designed to convert an internal payload agnostic Avalon Streaming data bus to MIPI/CSI2 data.

Base Features

- Provides Compatible MIPI D-Phy v1.1 physical layer using FPGA LVDS/LVCMOS IO and passive network

- Supports CSI-2 protocol for unidirectional data transfer

- Compatible with D-PHY Configured for 1 clock and 1 data lane

- Intended for per-lane clocks rates up to 1 Gbps, depending on device speed grade

- Generates single logical channel CSI-2 encapsulation, including:

- CSI-2 short packets [SOF,EOF,SOL,EOL]

- CSI-2 header and ECC field

- CSI-2 data CRC

- Transmits MIPI Packets including: LP to HS state transition, sync pattern, payload, and trailer

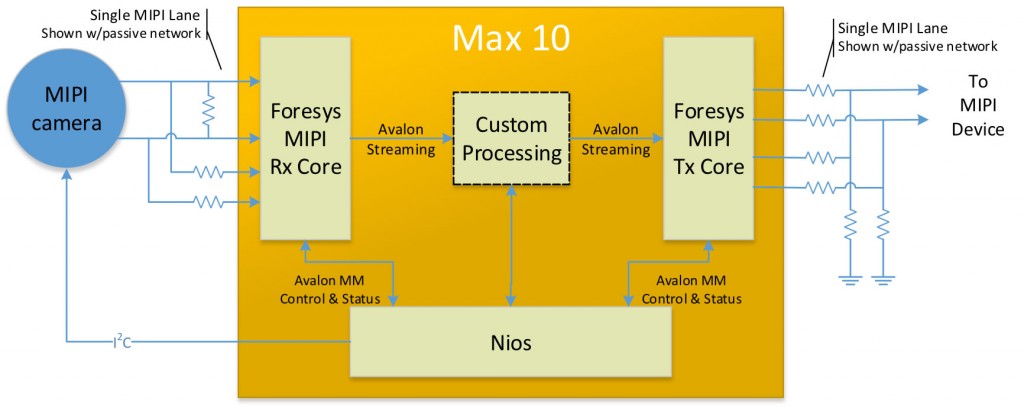

Example Application

This is a simple example of an Altera Max 10 FPGA being used to process image data being received by an Omnivision OV10640 MIPI camera Over the Foresys MIPI CSI2 Rx core and passing the resultant image data back out a MIPI TX interface using the Foresys MIPI CSI2 Tx core. In this example, the FPGA has access to the video stream and can sit between a MIPI camera and the its destination.